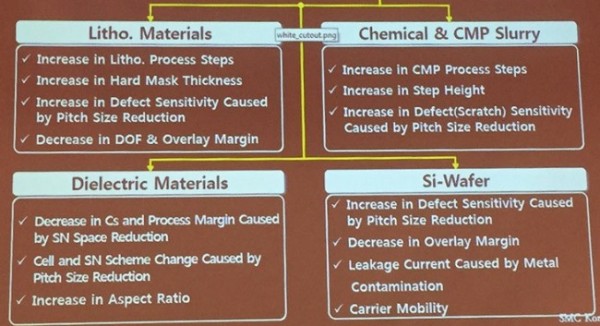

SK하이닉스가 소재 측면에서 해결해야 할 과제를 제시했다. 메모리 반도체는 선폭 미세화(Pitch Scale down) 때문에 공정 수가 늘어나면서 생산 비용이 증가하고 있다. 커패시터 바닥 면적과 높이 비율(Aspect Ratio)이 기하급수적으로 커지면서 수율도 여전히 발목을 잡고 있다.

바닥면적 대 높이 비율(A/R) 증가 문제

노광(리소그래피)에 쓰이는 하드마스크는 현재는 비정질탄소막(아몰포스 카본)을 쓰고 있지만 증착(CVD) 공정을 여러 번 거치면 생산성이 떨어진다는 단점이 있다. 다양한 에칭 공정을 견딜 수 있고, 두께가 두꺼워 커패시터를 수직방향으로 높이기 유리한 포토레지스터(PR)가 필요하다. 하지만 소재가 층층이 쌓이기 때문에 아래 부분까지 빔이 통과하기 위해서는 투명도가 높아야 한다. 상반된 특성을 어떻게 구현할 것인가가 관건이다.

유전체(Dielectric Materials)는 커패시터 면적을 줄여줄 수 있는 새로운 하이케이(High-K) 물질을 찾아야 한다. 그동안 게르마늄 기반 소재가 쓰였는데, 게르마늄 기반의 또다른 소재나 아예 다른 물질을 찾는 게 관건이다. 저장된 전자를 잘 담고 있을 수 있는 높은 일함수(Work-Function) 전극, 에칭 시간을 단축시켜줄 수 있는 에칭용 가스 등을 찾고 있다.

세정(클리닝) 공정에서는 커패시터를 쓰러뜨리지 않는(Leaning Free Chemical) 화학물질이 필요하다. WRC(wear-resistant coatings), 초임계 이산화탄소(sCO2)를 뛰어넘을 수 있는 소재를 발굴해야 한다.

공정 미세화, 공정 비용을 줄여라

D램은 20나노미터(nm) 이하 공정을 도입하면서 노광(리소그래피) 공정이 늘어나고 있다. 웨이퍼에 반도체 회로를 그릴 때 공정을 두번 반복하는 '더블패터닝기술(DPT)'을 이용해 미세 선폭을 구현하기 때문이다.

20·22nm 등 20nm 초반 D램에 DPT 기술을 사용하면 30nm에 비해 증착·에칭 작업 단계가 3.5배 늘어난다. 생산 시간이 길어지고 장비 투자비용도 증가한다.

SK하이닉스는 리소그래피 공정용 소재에 '3H'를 요구한다. 고성능(High Performance), 고생산성(High Productivity), 양질(High Quality)을 통칭하는 말이다.

포토레지스터(PR)는 매끈하게 선을 그릴 수 있고(Line Width Roughness), 초점심도(DOF) 공정 마진을 개선 시킬 수 있는, 활성에너지가 낮은 소재를 적용하기를 원했다. 공정 단계를 축소시킬 수 있는 소재, 평탄화 소재도 필요하다. 배치간 특성 변화(Batch to Batch Variation) 를 최소화 시킬 수 있는 물질, 고효율 여과시스템, 원재료로부터 고순도 물질을 정제하는 시스템을 구축해야 한다. 안명훈 SK하이닉스 수석은 "소재별로 맞는 필터를 사용하는지, 원재료를 잘 정제했는지 등도 반도체 품질에 상당한 영향을 준다"고 말했다.

안 수석은 "유전체 질을 높이기 위해 2차 협력업체 관리가 중요하다"고 역설했다. 원재료를 공급받을 때부터 질 관리에 들어가야 한다는 것. 소재 스펙(spec)에는 없지만 품질에 영향을 미칠 수 있는 다양한 요소들을 모니터링하는 시스템까지 갖출 것을 소재 협력업체에 요구했다.

긁힘이 적은 CMP슬러리와 수명이 긴 CMP 패드 등을 개발하는 것도 과제로 꼽혔다.